|

|

Program

Keynote 1: DARPA's Data Driven Discovery of Models (D3M) and Software Defined Hardware (SDH) programs

(Water Tower AB - Floor 2, 9:00 - 10:00, Wednesday, May 23)

Wade Shen, Program Manager, DARPA

Moderator: Houman Homayoun, George Mason University

Abstract:

This talk will provide background and understand on two nationally significant DARPA programs.

D3M:

Understanding the complex and increasingly data-intensive world around us relies on the

construction of robust empirical models, i.e., representations of real, complex systems

that enable decision makers to predict behaviors and answer “what-if” questions. Today,

construction of complex empirical models is largely a manual process requiring a team of

subject matter experts and data scientists. With ever more data becoming available via

improved sensing and open sources, the opportunity exists to build models to speed scientific

discovery, enhance Department of Defense/Intelligence Community’s intelligence, and improve

United States Government logistics and workforce management, but capitalizing on this

opportunity is fundamentally limited by the availability of data scientists.

The Data-Driven Discovery of Models (D3M) program aims to develop automated model discovery

systems that enable users with subject matter expertise but no data science background to

create empirical models of real, complex processes. This capability will enable subject

matter experts to create empirical models without the need for data scientists, and will

increase the productivity of expert data scientists via automation.

SDH:

In modern warfare, decisions are driven by information. The ability to provide useful

understanding and prediction is dependent on the efficient implementation of algorithms.

Today, to gain the most efficiency possible, we design and fabricate application specific

integrated circuits (ASICs) to maximize the efficiency of a specific algorithm. ASICs typically

cost hundreds of millions of dollars and take many years to develop, and they can perform

exactly one specific algorithm. Because ASICs are so specifically tailored and costly,

they are viable only for the highest priority applications. For problems that cannot afford

this level of investment, compute efficiency is sacrificed by implementing solutions on

general-purpose processors or field programmable gate arrays (FPGAs). Typically, this

results in application implementations that are thousands of times worse than optimal.

The Software Defined Hardware (SDH) program aims to develop a malleable hardware/software

architecture that enables near ASIC performance without sacrificing programmability for

data-intensive algorithms. SDH will enable multiple data-intensive algorithms to run at

near ASIC efficiency on a single architecture without the cost, development time or single

application limitations associated with ASICs or the inefficiencies associated with general

purpose processing. SDH architectures can be reused for new problems and new algorithms for

existing problems, and the dynamic optimization of code and hardware when input data change.

Bio:

Mr. Wade Shen joined DARPA in 2014 as a program manager. His research

interests include machine learning, machine translation, speech recognition and data analytics

for improved human/computer interaction. Mr. Shen joined DARPA from the Massachusetts Institute

of Technology, Lincoln Laboratory where he was an associate group leader in the Human Language Technology Group. Mr. Shen’s area of research involved machine translation; speech; speaker and language recognition; information extraction and prosodic modeling for both small- and large-scale applications. Prior to joining MIT Lincoln Laboratory, Wade helped found and served as chief technology officer for Vocentric Corporation, a company specializing in speech technologies for resource-constrained and embedded applications. Mr. Shen has served as the chair of Lincoln

Laboratory's Advanced Concept Committee, on DARPA's Information Science and Technology (ISAT)

study group and as the US technical representative for NATO's IST-078 and IST-102 speech/language

processing study groups.

Mr. Shen received his master's degree in computer science from the University of Maryland,

College Park and his bachelor's degree in electrical engineering and computer science from the

University of California, Berkeley.

|

Keynote 2: Self-Awareness for Heterogeneous MPSoCs: A Case Study using Adaptive, Reflective Middleware

(Water Tower AB - Floor 2, 9:00 - 10:00, Thursday, May 24)

Nikil Dutt, Chancellor’s Professor, University of California, Irvine

Moderator: Baris Taskin, Drexel University

Abstract:

Self-awareness has a long history in biology, psychology, medicine,

engineering and (more recently) computing. In the past decade this has inspired new self-aware

strategies for emerging computing substrates (e.g., complex heterogeneous MPSoCs) that must cope

with the (often conflicting) challenges of resiliency, energy, heat, cost, performance, security,

etc. in the face of highly dynamic operational behaviors and environmental conditions. Earlier we

had championed the concept of CyberPhysical-Systems-on-Chip (CPSoC), a new class of sensor-actuator

rich many-core computing platforms that intrinsically couples on-chip and cross-layer sensing and

actuation to enable self-awareness. Unlike traditional MPSoCs, CPSoC is distinguished by an

intelligent co-design of the control, communication, and computing (C3) system that interacts

with the physical environment in real-time in order to modify the system’s behavior so as to

adaptively achieve desired objectives and Quality-of-Service (QoS). The CPSoC design paradigm

enables self-awareness (i.e., the ability of the system to observe its own internal and external

behaviors such that it is capable of making judicious decision) and (opportunistic) adaptation

using the concept of cross-layer physical and virtual sensing and actuations applied across

different layers of the hardware/software system stack. The closed loop control used for adaptation

to dynamic variation -- commonly known as the observe-decide-act (ODA) loop -- is implemented using

an adaptive, reflective middleware layer.

In this talk I will present a case study of this adaptive, reflective middleware layer using a

holistic approach for performing resource allocation decisions and power management by leveraging

concepts from reflective software. Reflection enables dynamic adaptation based on both external feedback

and introspection (i.e., self-assessment). In our context, this translates into performing resource

management actuation considering both sensing information (e.g., readings from performance counters,

power sensors, etc.) to assess the current system state, as well as models to predict the behavior of

other system components before performing an action. I will summarize results leveraging our

adaptive-reflective middleware toolchain to i) perform energy-efficient task mapping on heterogeneous

architectures, ii) explore the design space of novel HMP architectures, and iii) extend the lifetime of

mobile devices.

Bio:

Dr. Nikil Dutt is a Chancellor's Professor of CS, Cognitive Sciences, and

EECS at the University of California, Irvine. He received a PhD from the University of Illinois

at Urbana-Champaign (1989). His research interests are in embedded systems, EDA, computer

architecture and compilers, distributed systems, and brain-inspired architectures and computing.

He has received numerous best paper awards and is coauthor of 7 books. Professor Dutt has served

as EiC of ACM TODAES and AE for ACM TECS and IEEE TVLSI. He is on the steering, organizing, and

program committees of several premier EDA and Embedded System Design conferences and workshops,

and has also been on the advisory boards of ACM SIGBED, ACM SIGDA, ACM TECS and IEEE ESL. He is an

ACM Fellow, IEEE Fellow, and recipient of the IFIP Silver Core Award.

|

Keynote 3: Assuring Microelectronics Innovation for National Security & Economic Competitiveness (MINSEC)

(Glessner ABC - Floor 3, 12:00 - 1:10, Thursday, May 24)

Jeremy Muldavin, Deputy Director of Defense Software & Microelectronics Activities, Office of the Deputy Assistant Secretary of Defense for Systems Engineering

Moderator: Houman Homayoun, George Mason University

Abstract:

The Office of the Deputy Assistant Secretary of Defense for Systems Engineering

launched an initiative in Fiscal Year (FY) 2017 in support of trusted and assured access to advanced

semiconductor technology for the Department of Defense (DoD) as well as the broader United States Government.

The initiative has three main elements: (1) development of an alternate trusted photomask capability to preserve

long-term trusted access and protection of Intellectual Property, (2) enhanced verification and validation

activities at key government laboratories and the promotion of industry best practices and commercial standards in

the areas of microelectronics trust and assurance, and (3) the development and transition of technologies in

support of a new trust and assurance approach. In recognition of critical near term needs, the DoD requested

additional funding in FY 2018 to address gaps in availability, access, and assurance including an initial

investment in next generation disruptive microelectronics research and development to maintain U.S.

technological edge in critical technology and the marketplace. This presentation will describe these efforts

and discuss their status and the overarching management approach.

Bio:

Dr. Jeremy Muldavin received his BSE in Engineering Physics and his MSE

and PHD in Electrical Engineering with a major in Electromagnetics and a minor in

Communications. He has worked at MIT Lincoln Laboratory since 2001 researching advanced

microelectronics, semiconductor fabrication, embedded systems, and open and distributed

architectures. He is currently on an IPA assignment to the Office of the Deputy Assistant

Secretary of Defense for Systems Engineering (ODASD (SE)), where he serves as Deputy Director

assigned to address near-term and longer term access to trusted and assured foundry capabilities.

|

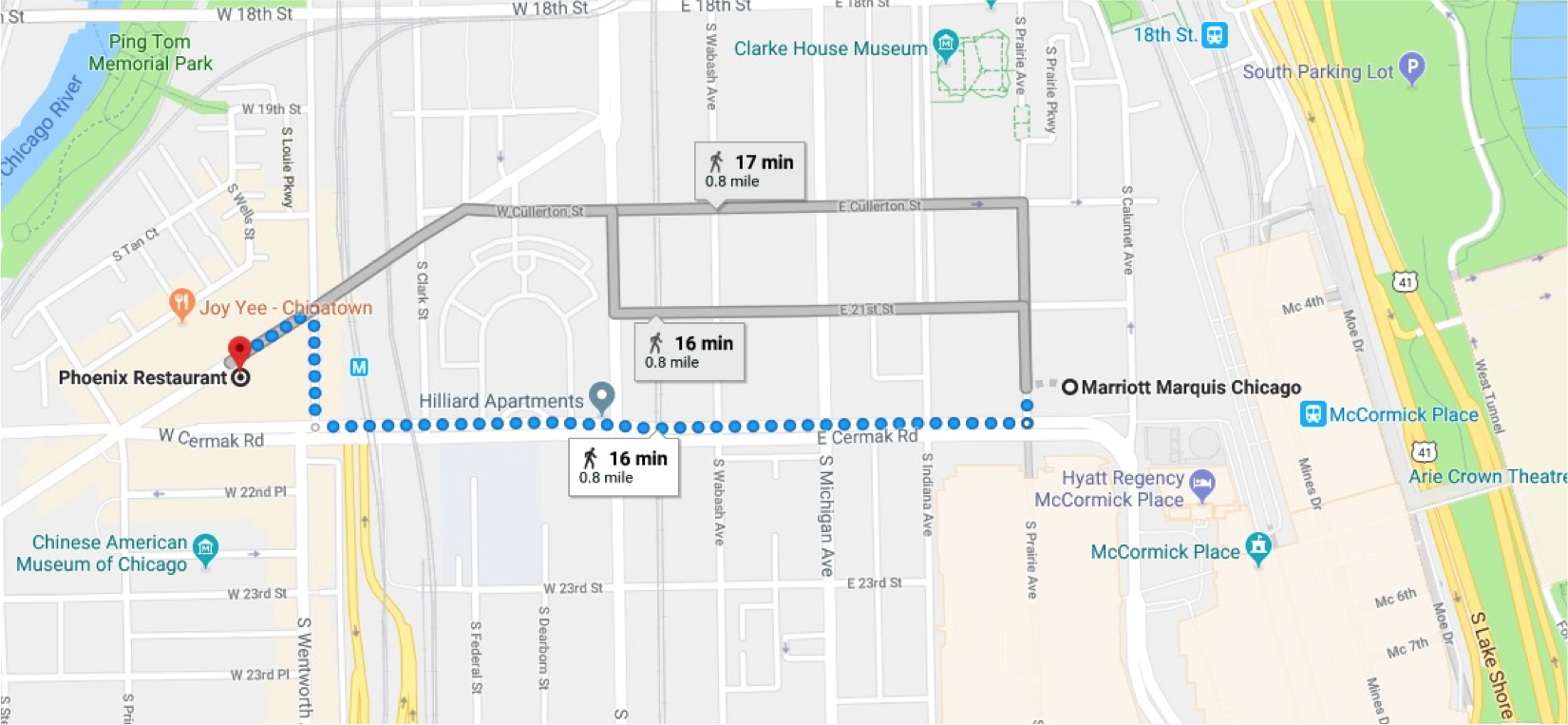

Keynote 4: Connected Devices, AI, and Scale – Trends Driving Semiconductor Innovation

(Phoenix Restaurant / Chinatown, 07:00 - 9:30, Thursday, May 24)

David Pellerin, Head of Global Business Development, Infotech/Semiconductor, Amazon Web Services

Moderator: Deming Chen, University of Illinois at Urbana–Champaign

Abstract:

Rapid adoption and production deployments of connected devices,

coupled with AI-driven methods of advanced analytics, have led to an explosion in demand for

non-traditional, more scalable computing and data management platforms. This increasing demand is

being seen in the public cloud as well as in cloud-connected IoT edge devices. AI is at the heart of

many the newest, most advanced analytics and IoT applications, ranging from robotics and autonomous

vehicles, to cloud-connected products such as Amazon Alexa, to smart factories and consumer-facing

services in the financial and healthcare sectors. This talk presents examples of such use-cases within

Amazon, as well examples of how Amazon customers increasingly rely on AI coupled with IoT hardware and

software stacks to innovate faster, and at cloud scales. The talk will conclude with examples of how

cloud-based semiconductor design and manufacturing are being enhanced using these same methods.

Bio:

Mr. David Pellerin serves as Head of Worldwide Business Development for Infotech/Semiconductor

at Amazon Web Services. Prior to joining AWS, Mr. Pellerin had a career in electronic design automation and

hardware-accelerated reconfigurable computing. He has experience with digital logic simulation and optimization,

high-level synthesis, grid and cluster computing, FPGA design, and embedded systems. He has published five

Prentice Hall technical books including “Practical Design Using Programmable Logic”, “VHDL Made Easy”,

and “Practical FPGA Programming in C”.

|

Keynote 5: A Cross-Layer Perspective for Energy Efficient Processing - From beyond-CMOS devices to deep learning

(Water Tower AB - Floor 2, 9:00 - 10:00, Friday, May 25)

X. Sharon Hu, Professor, University of Notre Dame

Moderator: Yanjing Li, University of Chicago

Abstract:

As Moore’s Law based device scaling and accompanying performance

scaling trends are slowing down, there is increasing interest in new technologies and

computational models for fast and more energy-efficient information processing. Meanwhile,

there is growing evidence that, with respect to traditional Boolean circuits and von Neumann

processors, it will be challenging for beyond-CMOS devices to compete with the CMOS technology.

Nevertheless, some beyond-CMOS devices demonstrate other unique characteristics such as ambipolarity,

negative differential resistance, hysteresis, and oscillatory behavior. Exploiting such unique

characteristics, especially in the context of alternative circuit and architectural paradigms,

has the potential to offer orders of magnitude improvement in terms of power, performance and

capability.

In order to take full advantage of beyond-CMOS devices, however, it is no longer sufficient to

develop algorithms, architectures and circuits independent of one another. Cross-layer efforts

spanning from devices to circuits to architectures to algorithms are indispensable. This talk will

examine energy-efficient neural network accelerators for embedded applications in this context.

Several deep neural network accelerator designs based on cross-layer efforts spanning from alternative

device technologies, circuit styles and architectures will be highlighted. A comprehensive

application-level benchmarking study for the MNIST dataset will be presented. The discussions will

demonstrate that cross-layer efforts indeed can lead to orders of magnitude gain towards achieving

extreme scale energy-efficient processing.

Bio:

Dr. X. Sharon Hu is a professor in the department of Computer Science and

Engineering at the University of Notre Dame, USA. Her research interests include low-power system

design, circuit and architecture design with emerging technologies, hardware/software co-design and

real-time embedded systems. She has published more than 300 papers in these areas. Some of her

recognitions include the Best Paper Award from the Design Automation Conference and from the IEEE

Symposium on Nanoscale Architectures, and the NSF CAREER award. She has participated in several

large government and industry sponsored center-level projects and is a theme leader in an NSF/SRC

E2CDA project. She is the General Chair of Design Automation Conference (DAC) in 2018, was the TPC

chair of DAC in 2015, and was a member of TPC and Executive Committees of a number of other conferences.

She also served as Associate Editor for IEEE Transactions on VLSI, ACM Transactions on Design Automation

of Electronic Systems, etc. and is an Associate Editor of ACM Transactions on Cyber-Physical Systems. X.

Sharon Hu is a Fellow of the IEEE.

|

Technical Sessions 1

Wednesday

May 23

10:20 - 12:00

|

Tech session 1: Emerging Computing, and Post-CMOS Technologies

(Water Tower AB - Floor 2)

Chair: Ronald Demara, University of Central Florida

Co-Chair: Mahdi Nikdast, Colorado State University

Logic-Encrypted Synthesis for Energy-Harvesting-Powered Spintronic-Embedded Datapath Design

Arman Roohi, Ramtin Zand and Ronald Demara

Low-Energy Deep Belief Networks using Intrinsic Sigmoidal Spintronic-based Probabilistic Neurons

(Best Paper Award Candidate)

Ramtin Zand, Kerem Y. Camsari, Steven D. Pyle, Ibrahim Ahmed, Chris H. Kim and Ronald F. Demara

Maxflow: Minimizing Latency in Hybrid Stochastic-Binary Systems

Paishun Ting and John Hayes

Methodology to Capture Statistical Effect of Process Imperfections on Glitch Suppression in CNFET circuits and Counter using Approximate Circuits

Kaship Sheikh and Lan Wei

Performance and Energy Enhancement Through an Online Single/Multi level mode Switching Cache Architecture

Ramin Rezaeizadeh Rookerd, Somayeh Sadeghi-Kohan and Zainalabedin Navabi

|

|

Technical Sessions 2

Wednesday

May 23

10:20 - 12:00

|

Tech session 2: Secure Design of Multi-Core and Cryptographic Systems

(George Pullman - Floor 3)

Chair: Sai Manoj, George Mason University

Co-Chair: Selcuk Kose, University of South Florida

SEPUFSoC: Using PUFs for Memory Integrity andAuthentication in Multi-Processors System-on-Chip

Johanna Sepulveda, Felix Willgerodt and Michael Pehl

Protecting Communication in Many-Core Systems against Active Attackers

Sadia Moriam, Elke Franz, Paul Walther, Akash Kumar, Thorsten Strufe and Gerhard Fettweis

A Homomorphic Encryption Scheme Based on Affine Transforms

Kyle Loyka, He Zhou and Sunil Khatri

Resilient AES Against Side-Channel Attack Using All-Spin Logic

Qutaiba Alasad, Jiann-Shiun Yuan and Jie Lin

|

|

Technical Sessions 3

Wednesday

May 23

1:10 - 2:30

|

Tech session 3: Interconnects and Manycore Management

(Water Tower AB - Floor 2)

Chair: Sudeep Pasricha, Colorado State University

Co-Chair: Anup Das, Drexel University

DeEPeR: Enhancing Performance and Reliability in Chip-Scale Optical Interconnection Networks

(Best Paper Award Candidate)

Mahdi Nikdast, Gabriela Nicolescu, Jelena Trajkovic and Odile Liboiron-Ladouceur

A 0.24pJ/bit, 16Gbps OOK Transmitter Circuit in 45-nm CMOS for Inter and Intra-Chip Wireless Interconnects

Tanmay Shinde, Suryanarayanan Subramaniam, Padmanabh Deshmukh, M Meraj Ahmed, Mark Indovina and Amlan Ganguly

TaSaT: Thermal-Aware Scheduling and Tuning Algorithm for Heterogeneous and Configurable Embedded Systems

Mohamad Hammam Alsafrjalani and Tosiron Adegbija

Interfacing 3D-stacked Electronic and Optical NoCs with Mixed CMOS-ECL Bridges: a Realistic Preliminary Assessment

Mahdi Tala, Oliver Schrape, Milos Krstic and Davide Bertozzi

|

|

Technical Sessions 4

Wednesday

May 23

4:40 - 6:00

|

Tech session 4: Low Power Variation Aware Circuit Design

Session chair: Inna Partin-Vaisband, University of Illinois at Chicago

(Water Tower AB - Floor 2)

Chair: Inna Partin-Vaisband, University of Illinois at Chicago

Co-Chair: Avesta Sasan, George Mason University

A Framework Exploiting Process Variability To Improve Energy Efficiency in FPGA Applications

Konstantinos Maragos, George Lentaris, Ioannis Stratakos and Dimitrios Soudris

Assessing the impact of temperature and supply voltage variations in near-threshold circuits using an analytical model

Sneh Saurabh and Vishav Vikash

Impolite High Speed Interfaces with Asynchronous Pulse Logic

Merritt Miller, Carrie Segal, David McCarthy, Aditya Dalakoti, Forrest Brewer and Prashansa Mukim

Short-path Padding Method for Timing Error Resilient Circuits based on Transmission Gates Insertion

(Best Paper Award Candidate)

Wentao Dai, Weiwei Shan and Peiye Liu

|

|

Technical Sessions 5

Thursday

May 24

10:20 - 12:00

|

Tech session 5: The World of Neural Networks

(Water Tower AB - Floor 2)

Chair: Amlan Ganguly, Rochester Institue of Technology

Co-Chair: Ioannis Savidis, Drexel University

Energy and Performance Efficient Computation Offloading for Deep Neural Networks in a Mobile Cloud Computing Environment

Amir Erfan Eshratifar and Massoud Pedram

Adapting Convolutional Neural Networks for Indoor Localization with Smart Mobile Devices

(Best Paper Award Candidate)

Ayush Mittal, Saideep Tiku and Sudeep Pasricha

Face Recognition with Hybrid Efficient Convolution Algorithms on FPGAs

Chuanhao Zhuge, Xinheng Liu, Xiaofan Zhang, Sudeep Gummadi, Jinjun Xiong and Deming Chen

SCALENet: a SCalable Low power AccELerator for real-time embedded deep neural Networks

Colin Shea, Adam Page and Tinoosh Mohsenin

|

|

Technical Sessions 6

Thursday

May 24

1:10 - 2:30

|

Tech session 6: New Solutions for Classic IP Protection Challenges

(Water Tower AB - Floor 2)

Chair: Benjamin Carrion Schaefer, University of Texas at Dallas

Co-Chair: Hamid Mahmoodi, San Francisco State University

Improving the Security of Split Manufacturing Using a Novel BEOL Signal Selection Method

Suyuan Chen and Ranga Vemuri

A novel polymorphic gate based circuit fingerprinting technique

Tian Wang, Xiaoxin Cui, Dunshan Yu, Omid Aramoon, Timothy Dunlap, Gang Qu and Xiaole Cui

Cross-Lock: Dense Layout-Level Interconnect Locking using Cross-bar Architectures

(Best Paper Award Candidate)

Kaveh Shamsi, Meng Li, David Z. Pan and Yier Jin

SRCLock: A SAT Resistance Cyclic Logic Obfuscation

Shervin Roshanisefat, Hadi Mardani Kamali and Avesta Sasan

|

|

Technical Sessions 7

Thursday

May 24

1:10 - 2:30

|

Tech session 7: Machine Learning and HW Accelerators

(George Pullman - Floor 3)

Chair: Fatemeh Tehranipoor, San Francisco State University

Co-Chair: Qi Zhu, Northwestern University

Scalable Hardware Accelerator for Mini-Batch Gradient Descent

Sandeep Rasoori and Venkatesh Akella

MC3A: Markov Chain Monte Carlo ManyCore Accelerator

Lahir Marni, Morteza Hosseini and Tinoosh Mohsenin

AEAS - Towards High Energy-efficiency Design for OpenSSL Encryption Acceleration through HW/SW Co-design

Chunhua Xiao, Yuhua Xie and Lei Zhang

A Machine Learning Attack Resistant Dual-mode PUF

Qian Wang, Mingze Gao and Gang Qu

|

|

Technical Sessions 8

Thursday

May 24

4:40 - 6:00

|

Tech session 8: Scalable Simulation: Parallel and Approximate Computing

(Water Tower AB - Floor 2)

Chair: Tinoosh Mohsenin, University of Maryland Baltimore County

Co-Chair: Gang Qu, University of Maryland

A Distributed Power Grid Analysis Framework from Sequential Stream Graph

Chun-Xun Lin, Tsung-Wei Huang, Ting Yu and Martin Wong

A Distributed Parallel Random Walk Algorithm for Large-Scale Capacitance Extraction and Simulation

(Best Paper Award Candidate)

Mingye Song, Zhezhao Xu, Wei Xue and Wenjian Yu

A Fast and Fuzzy Functional Simulator of Inexact Arithmetic Operators for Approximate Computing Systems

Justine Bonnot, Karol Desnos, Maxime Pelcat and Daniel Menard

Battery-aware Design Exploration of Scheduling Policies for Multi-sensor Devices

Yukai Chen, Daniele Jahier Pagliari, Enrico Macii and Massimo Poncino

|

|

Technical Sessions 9

Friday

May 25

10:20 - 12:00

|

Tech session 9: Test and Fault Tolerance

(Water Tower AB - Floor 2)

Chair: Yier Jin, University of Florida

Co-Chair: Yanjing Li, University of Chicago

Accelerating Coverage Directed Test Generation for Functional Verification: A Neural Network-based Framework

Fanchao Wang, Hanbin Zhu, Pranjay Popli, Yao Xiao, Paul Bodgan and Shahin Nazarian

Effective In-Situ Chip Health Monitoring with Selective Monitor Insertion Along Timing Paths

Hadi Ahmadi Balef, Hamed Fatemi, Kees Goossens and Jose Pineda De Gyvez

Low Complexity Burst Error Correcting Codes to correct MBUs in SRAMs

Abhishek Das and Nur A. Touba

Loss is Gain: Shortening Data for Lifetime Improvement on Low-Cost ECC Enabled Consumer-Level Flash Memory

Yejia Di, Liang Shi, Congming Gao, Qiao Li and Chun Xue

A Novel Fault-Tolerant Last Level Cache to Improve Reliability at Near-Threshold Voltage

Wei Liu, Zhigang Wei and Wei Du

|

|

Technical Sessions 10

Friday

May 25

1:10 - 2:30

|

Tech session 10: Memory Architectures

(Water Tower AB - Floor 2)

Chair: Yongqiang Lyu, Tsinghua University

AB-Aware: Application Behavior Aware Management of Shared Last Level Caches

Suhit Pai, Newton Singh and Virendra Singh

Towards Near-Data Processing of Compare Operations in 3D-stacked memory

Palash Das and Hemangee Kapoor

Utility Aware Snoozy Caches for Energy Efficient Chip Multi-Processors

A. Kulkarni, Shounak Chakraborty, S. P. Mahajan and Hemangee K. Kapoor

SARO: A State-Aware Reliability Optimization Technique for High Density NAND Flash Memory

Myungsuk Kim, Youngsun Song, Myoungsoo Jung and Jihong Kim

|

|

Technical Sessions 11

Friday

May 25

1:10 - 2:30

|

Tech session 11: Modern Routing: from Timing, Reliability to Machine Learning

(George Pullman - Floor 3)

Chair: Yue Zhang, Beihang University

Simultaneous Timing Driven Tree Surgery in Routing with Machine Learning-based Acceleration

Peishan Tu, Chak-Wa Pui and Evangeline Young

Electromigration Design Rule aware Global and Detailed Routing Algorithm

Xiaotao Jia, Yici Cai, Qiang Zhou and Jing Wang

A Comparative Study of Local Net Modeling Using Machine Learning

Jackson Melchert, Boyu Zhang and Azadeh Davoodi

Fast Timing Analysis of Non-Tree Clock Network with Shorted Wires

Kiwon Yoon, Daijoon Hyun and Youngsoo Shin

|

|

Special Sessions 1

Wednesday

May 23

1:10 - 2:30

|

Special session 1: Powering Heterogeneous IoT Systems: Design for Efficiency, Security, and Sustainability

(George Pullman - Floor 3)

Organizers: Selcuk Kose, University of South Florida

Co-organizers: Inna Partin-Vaisband, University of Illinois at Chicago

Title 1: Reliable On-Chip Voltage Regulation for Sustainable and Compact IoT and Heterogeneous Computing Systems

Speaker: Selcuk Kose, University of South Florida

Title 2: Low-Energy Architectures of Linear Classifiers for IoT Applications using Incremental Precision and Multi-Level Classification

Speaker: Sandhya Koteshwarai, University of Minnesota at Twin Cities

Title 3: Towards A Universal Power Manager for Multi-Source Energy Scavenging and Storage

Speaker: Sudip K. Mazumder, University of Illinois at Chicago

Title 4: Efficient Wireless Power Transfer for Heterogeneous Adaptive IoT Systems

Speaker: Inna Partin-Vaisband, University of Illinois at Chicago

|

|

Special Sessions 2

Wednesday

May 23

4:40 - 6:00

|

Special session 2: Emergence of Silicon Photonics in High-Performance Computing: How can the VLSI Community Contribute

(George Pullman - Floor 3)

Organizer: Mahdi Nikdast, Colorado State University

Title 1: Low-Power Optical Interconnects based on Resonant Silicon Photonic Devices: Recent Advances and Challenges

Speaker: Meisam Bahadori, Columbia University

Title 2: Wavelength-Routed Optical Networks-on-Chip: Design Methods and Tools to Bridge the Gap Between Logic Topologies and Physical Ones in 3D Architectures

Speaker: Davide Bertozzi, University of Ferrara

Title 3: Cross-Layer Thermal Reliability Management in Silicon Photonic Networks-on-Chip

Speaker: Sudeep Pasricha, Colorado State University

Title 4: Silicon Photonic Interconnects: Minimizing the Controller Latency

Speaker: Gabriela Nicolescu, Polytechnique Montreal

|

|

Special Sessions 3

Thursday

May 24

10:20 - 12:00

|

Special session 3: Circuits and Systems for Autonomous IoT Devices

(George Pullman - Floor 3)

Organizer: Emre Salman, Stony Brook University

Co-organizer:Milutin Stanacevic, Stony Brook University

Title 1: Leveraging RF Power for Intelligent Tag Networks

Speaker: Milutin Stanacevic, Stony Brook University

Title 2: Quasi-self-powered Internet of Infrastructural Things: The Mackinac Bridge Case Study

Speaker: Kenji Aono, Washington University in St. Louis

Title 3: New GPR System Integration with Augmented Reality Based Positioning

Speaker: Tian Xia, University of Vermont

Title 4: MTJ Magnetization Switching Mechanisms for IoT Applications

Speaker: A. G. Qoutb, University of Rochester

Title 5: Structured Weight Matrices-Based Hardware Accelerators in Deep Neural Networks: FPGAs and ASICs

Speaker: Yanzhi Wang, Syracuse University

|

|

Special Sessions 4

Thursday

May 24

4:40 - 6:00

|

Special session 4: Implementing and Benchmarking Post-Quantum Cryptography in Hardware

(George Pullman - Floor 3)

Organizer: Kris Gaj, George Mason University

Title 1: Challenges and Rewards of Implementing and Benchmarking Post-Quantum Cryptography in Hardware

Speaker: Kris Gaj, George Mason University

Title 2: Physical Protection of Lattice-Based Cryptography - Challenges and Solutions

Speaker: Francesco Regazzoni, ALaRI - Università Della Svizzera Italiana

Title 3: Post-Quantum Cryptography on FPGAs: the Niederreiter Cryptosystem

Speaker: Wen Wang, Yale University

|

|

Special Sessions 5

Friday

May 25

10:20 - 12:00

|

Special session 5:

Artificial Intelligence at the Edge

(George Pullman - Floor 3)

Organizers: Cory Merkel, Air Force Research Lab

Co-organizers: Dhireesha Kudithipudi, Rochester Institute of Technology

Title 1: Going small: using the insect brain as a model system for edge processing applications

Speaker: Angel Yanguas-Gil, Argonne National Laboratory

Title 2: Energy and Area Efficiency in Neuromorphic Computing for Resource Constrained Devices

Speaker: Gangotree Chakma, University of Tennessee

Title 3: Mixed-Signal POp/J Computing with Nonvolatile Memories

Speaker: Mohammad Reza Mahmoodi, University of California, Santa Barbara

Title 4: Gate-Controlled Memristors and their Applications in Neuromorphic Architectures

Speaker: Eric Herrmann, University of Cincinnati

Title 5: Design Exploration of IoT centric Neural Inference Accelerators

Speaker: Vivek Parmar, Indian Institute of Technology

|

|

Special Sessions 6

Friday

May 25

2:30 - 3:30

|

Special session 6: Stochastic and Approximate Computing for Emerging Learning and Communication Systems

(Water Tower AB - Floor 2)

Organizers: Jie Han, University of Alberta

Co-organizers: Yue Zhang, Beihang University

Title 1: Leveraging Spintronic Devices for Efficient Approximate Logic and Stochastic Neural Networks

Speaker: Shaahin Angizi, University of Central Florida

Title 2: Design space exploration of magnetic tunnel junction based stochastic computing in deep learning

Speaker: You Wang, Beihang University

Title 3: A High-Efficiency Bit-Wise Iterative Decoder for Polar Codes using Stochastic Computing

Speaker: Warren J. Gross, McGill University

|

|

Panel Sessions 1

Wednesday

May 23

3:30 - 4:30

|

Panel Discussions 1. Low Power & Trusted Machine Learning

(Water Tower AB - Floor 2)

Organizer: Avesta Sasan, George Mason University

Panelist:

Qi Zhu, Northwestern University

Yanzhi Wang, Syracuse University

Jae-Sun Seo, Arizona State University

Tinoosh Mohsenin, University of Maryland

|

|

Panel Sessions 2

Thursday

May 24

3:30 - 4:30

|

Panel Discussions 2. Securing the Systems of the Future -- Techniques for a Shifting Attack Space

(Water Tower AB - Floor 2)

Organizer: Ioannis Savidis, Drexel University

Panelist:

Swarup Bhunia, University of Florida

Gang Qu, University of Maryland

Matthew Casto, Air Force Research Lab

Jeremy Muldavin, Office of the Deputy Assistant Secretary of Defense

|

|

Poster Sessions 1

Wednesday

May 23

2:30 - 3:30

|

Poster session 1:

(Daniel Burnahm AB - Floor 3)

Chair: Baris Taskin, Drexel University

Comparative Study of Approximate Multipliers

Mahmoud Masadeh, Osman Hasan and Sofiene Tahar

Dataflow-Based Mapping of Spiking Neural Networks on Neuromorphic Hardware

Anup Das and Akash Kumar

Design of Dynamic Range Approximate Logarithmic Multipliers

Peipei Yin, Chenghua Wang, Weiqiang Liu and Fabrizio Lombardi

Investigation and Optimization of Pin Multiplexing in High-Level Synthesis

Shuangnan Liu, Francis Lau and Benjamin Carrion Schafer

Energy Consumption and Lifetime Improvement of Coarse-Grained Reconfigurable Architectures Targeting Low-Power Error-Tolerant Applications

Hassan Afzali-Kusha, Omid Akbari, Mehdi Kamal and Massoud Pedram

MuDBN: An Energy-Efficient and High-Performance Multi-FPGA Accelerator for Deep Belief Networks

Yuming Cheng, Chao Wang, Yangyang Zhao, Xianglan Chen, Xuehai Zhou and Xi Li

Performance Impact of Emerging Memory Technologies on Big Data Applications: A Latency-Programmable System Emulation Approach

Mu-Tien Chang, I. Stephen Choi, Dimin Niu and Hongzhong Zheng

BiNMAC: Binarized neural Network Manycore Accelerator

Ali Jafari, Seyed-Morteza Hosseini, Adwaya Kulkarni and Tinoosh Mohsenin

A Hybrid Approach to Equivalent Fault Identification for Verification Environment Qualification

Chia-Cheng Wu, Tung-Yuan Lee, Yung-An Lai, Hsin-Pei Wang, De-Xuan Ji, Yan-Ping Chang, Teng-Chia Wang, Chin-Heng Liu, Chun-Yao Wang and Yung-Chih Chen

Memristive Crossbar Mapping for Neuromorphic Computing Systems on 3D IC

Qi Xu, Song Chen, Bei Yu and Feng Wu

Impact of Aging on Template Attacks

Naghmeh Karimi, Sylvain Guilley and Jean-Luc Danger

MUCH-SWIFT: A High-Throughput Multi-Core HW/SW Co-design K-means Clustering Architecture

Hadi Mardani Kamali and Avesta Sasan

|

|

Poster Sessions 2

Thursday

May 24

2:30 - 3:30

|

Poster session 2:

(Daniel Burnahm AB - Floor 3)

Chair: Houman Homayoun, George Mason University

An Efficient Cache Management Scheme for Capacitor Equipped Solid State Drives

Congming Gao, Liang Shi, Yejia Di, Qiao Li, Chun Xue and H.M. Edwin Sha

Evaluation of the Complexity of Automated Trace Alignment using Novel Power Obfuscation Methods

Bozhi Liu, Kemeng Chen, Minjun Seo, Janet Roveda and Roman Lysecky

A CMOS Low power 4th-Order Delta-Sigma Modulator with one reconfigurable amplifier

Jae Hyeon Seong and Kwang Yoon

On the Design of Reliable Heterogeneous Systems via Checkpoint Placement and Core Assignment

Edwin Sha, Hailiang Dong, Weiwen Jiang, Qingfeng Zhuge, Xianzhang Chen and Lei Yang

SAT-Lancer: A Hardware SAT-Solver for Self-Verification

Buse Ustaoglu, Sebastian Huhn, Daniel Große and Rolf Drechsler

FLexiTASK: A Flexible FPGA Overlay for Efficient Multitasking

Joel Mandebi Mbongue, Danielle Tchuinkou Kwadjo and Christophe Bobda

An architectural support for reduction of in-rush current in systems with instruction controlled power gating

Sumanta Pyne

Optimal Topology-Aware PV Panel Floorplanning with Hybrid Orientation

Sara Vinco, Enrico Macii and Massimo Poncino

ADDHard: Arrhythmia Detection on Digital Hardware by Learning ECG Signal

Sai Manoj Pudukotai Dinakarrao

Conditional All Error Detection and Correction for the Internal Stages of AES Hardware Implementation

Lake Bu and Michel Kinsy

Parsim: Simulation Infrastructure for Exploring Thousands of Cores

Tim Grant, Konstantin Shkurko, Erik Brunvand, Daniel Kopta and Josef Spjut

Static Design of Spin Transfer Torques Magnetic Look Up Tables for ASIC Designs

Aliyar Attaran, Tyler Sheaves, Praveen Mugula and Hamid Mahmoodi

|

|

Network Events

Thursday’s Banquet, 7-9PM

With Banquet Keynote

At Phoenix Restaurant: 2131 S Archer Ave, Chinatown

|

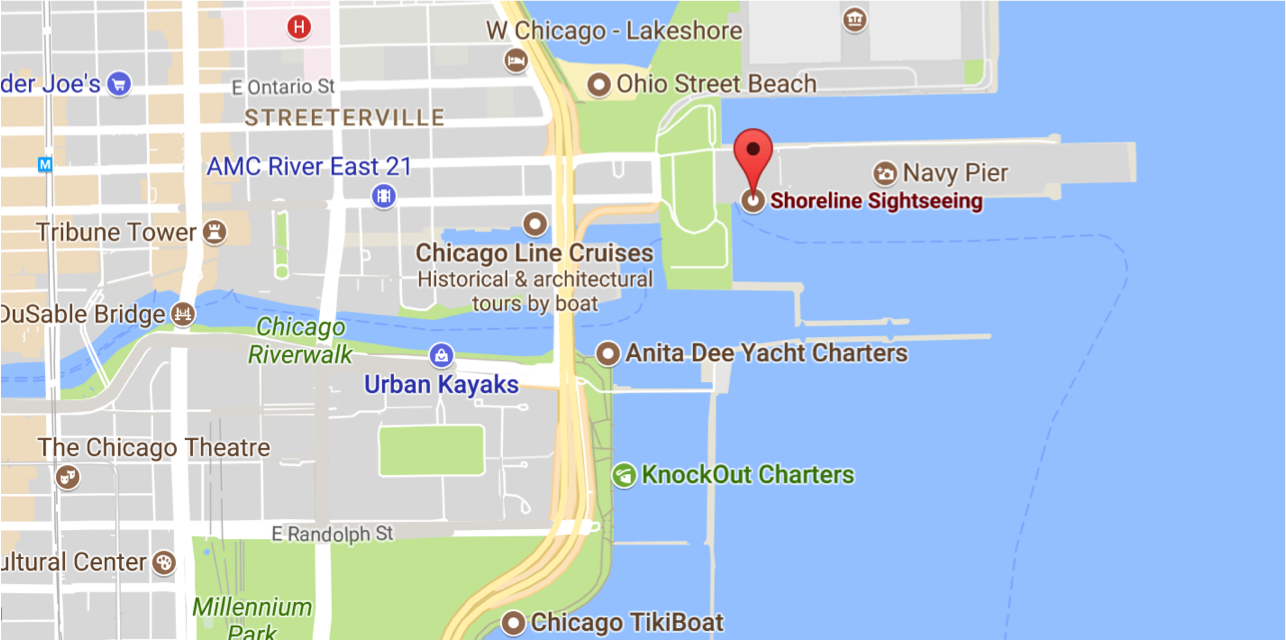

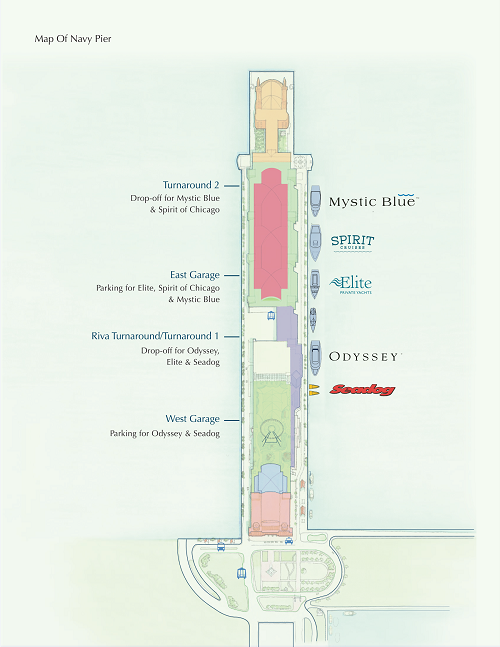

Friday’s Boat Tour, 5PM

Locaton (Navy Pier): 600 E Grand Ave, Chicago, IL 60611

Tour lasts about 75 mins (Link)

Highlights: Tribune Tower, Wrigley Building, Trump Tower, Willis Tower

Price: $20

|

This site is maintained by:

GLSVLSI 2018 Webmaster

Yi-Chung Chen (cheny@newpaltz.edu),

SUNY at New Paltz.

|